# **Numerically Controlled Oscillator IP Core User's Guide**

# **Table of Contents**

| Chapter 1. Introduction                                      | 4  |

|--------------------------------------------------------------|----|

| Quick Facts                                                  |    |

| Features                                                     | 8  |

| Chapter 2. Functional Description                            | 10 |

| Principle of NCO                                             |    |

| Lattice NCO Implementation                                   |    |

| Sum-of-Angles Memory Reduction                               |    |

| Improving Quality of Output                                  |    |

| Multi-channel NCO                                            |    |

| Quadrature Amplitude Modulation (QAM)                        |    |

| Signal Descriptions                                          |    |

| Latency                                                      |    |

| Timing Diagrams                                              |    |

| Chapter 3. Parameter Settings                                |    |

| Architecture Tab                                             |    |

| Multi-channel Mode                                           |    |

| Wave Characteristics                                         |    |

| Phase Correction                                             |    |

| QAM Mode                                                     |    |

| FSK/PSK Tab                                                  |    |

| FSK Mode                                                     |    |

| PSK Mode                                                     |    |

| Implementation Tab                                           |    |

| Memory Type                                                  |    |

| DSP Block                                                    |    |

| Data Output Ports                                            |    |

| Optional I/O Ports                                           |    |

| Pipeline Tab                                                 |    |

| Pipeline Options                                             |    |

| Summary Tab                                                  |    |

| Chapter 4. IP Core Generation                                |    |

| Licensing the IP Core                                        |    |

| Getting Started                                              |    |

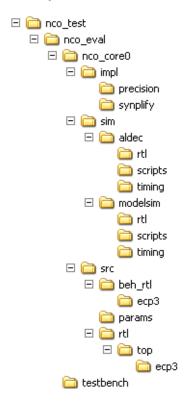

| IPexpress-Created Files and Top Level Directory Structure    |    |

| Instantiating the Core                                       |    |

| Running Functional Simulation                                |    |

| Synthesizing and Implementing the Core in a Top-Level Design |    |

| Hardware Evaluation                                          |    |

| Enabling Hardware Evaluation in Diamond:                     |    |

| Enabling Hardware Evaluation in ispLEVER:                    |    |

| Updating/Regenerating the IP Core                            |    |

| Regenerating an IP Core in Diamond                           |    |

| Regenerating an IP Core in ispLEVER                          |    |

| Chapter 5. Support Resources                                 |    |

| Lattice Technical Support                                    |    |

| Online Forums                                                |    |

| Telephone Support Hotline                                    |    |

| E-mail Support                                               |    |

| Local Support                                                |    |

| בייטמו טעףף∪ונ                                               |    |

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Internet                         | 35 |

|----------------------------------|----|

| References                       | 35 |

| LatticeECP/EC                    | 35 |

| LatticeECP2M                     | 35 |

| LatticeECP3                      | 35 |

| LatticeSC/M                      | 36 |

| LatticeXP                        | 36 |

| LatticeXP2                       | 36 |

| Revision History                 | 36 |

| Appendix A. Resource Utilization |    |

| LatticeEC Devices                | 37 |

| Ordering Part Number             | 37 |

| LatticeECP Devices               | 38 |

| Ordering Part Number             | 38 |

| LatticeECP2 Devices              | 39 |

| Ordering Part Number             | 39 |

| LatticeECP2M Devices             | 39 |

| Ordering Part Number             | 39 |

| LatticeECP3 Devices              | 40 |

| Ordering Part Number             | 40 |

| LatticeSC/M Devices              | 40 |

| Ordering Part Number             | 40 |

| LatticeXP Devices                | 40 |

| Ordering Part Number             | 40 |

| LatticeXP2 Devices               | 41 |

| Ordering Part Number             | 41 |

|                                  |    |

# Introduction

Numerically Controlled Oscillators (NCO), also called Direct Digital Synthesizers (DDS), offer several advantages over other types of oscillators in terms of accuracy, stability and reliability. NCOs provide a flexible architecture that enables easy programmability such as on-the-fly frequency/phase. NCOs are used in many communications systems including:

- Digital up/down converters used in 3G wireless and software radio systems

- Digital PLLs

- RADAR systems

- · Drivers for optical or acoustic transmissions

- Multilevel FSK/PSK modulators/demodulators

Lattice provides a parameterizable NCO IP core that supports multiple channels and a Quadrature Amplitude Modulation (QAM) mode, in addition to other usual configurations. The resource utilization and performance trade-off can be tuned by configuring different parameters of the IP core to obtain the optimal Spurious Free Dynamic Range (SFDR) result. The Lattice NCO core offers a variety of memory reduction schemes and mechanisms for SFDR improvement.

# **Quick Facts**

Table 1-1 through Table 1-9 give quick facts about the NCO IP core for LatticeEC™, LatticeECP™, LatticeECP™, LatticeSC™, LatticeSCM™, LatticeXP™, LatticeECP2M™, LatticeXP2™, and Lattice ECP3™ devices.

Table 1-1. NCO IP core for LatticeEC Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                 |                                                                  |

|-------------------------|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |

| Core                    | FPGA Families Supported | LatticeEC                                                       |                                                                 |                                                                  |

| Requirements            | Minimal Device Needed   | LFEC3E                                                          | LFEC1E                                                          | LFEC6E                                                           |

|                         | Targeted Device         | LFEC20E-5F672C                                                  |                                                                 |                                                                  |

| _                       | LUTs                    | 1800                                                            | 300                                                             | 3800                                                             |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 2                                                               | 5                                                                |

|                         | Registers               | 800                                                             | 300                                                             | 1900                                                             |

|                         | MULT18X18ADDSUB         |                                                                 | N/A                                                             |                                                                  |

|                         | Lattice Implementation  | Dia                                                             | mond <sup>®</sup> 1.0 or ispLEVER <sup>®</sup> 8                | 3.1                                                              |

| Design Tool             | Synthesis               | Synopsys <sup>®</sup> S                                         | Synplify® Pro for Lattice D-                                    | 2009.12L-1                                                       |

| Support                 | Simulation              | Aldec® Active-HD® 8.2 Lattice Edition II                        |                                                                 |                                                                  |

|                         | Jiiiulalion             | Mentor Graphics® ModelSim® SE 6.3F                              |                                                                 | 6.3F                                                             |

Table 1-2. NCO IP core for LatticeECP Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |  |

| Core                    | FPGA Families Supported |                                                                 | LatticeECP                                                         |                                                                  |  |

| Requirements            | Minimal Device Needed   | LFECP6E                                                         |                                                                    |                                                                  |  |

|                         | Targeted Device         | LFECP20E-5F672C                                                 |                                                                    |                                                                  |  |

| _                       | LUTs                    | 100                                                             | 300                                                                | 400                                                              |  |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 2                                                                  | 5                                                                |  |

|                         | Registers               | 100                                                             | 300                                                                | 500                                                              |  |

|                         | MULT18X18ADDSUB         | 2                                                               | 0                                                                  | 4                                                                |  |

|                         | Lattice Implementation  | Diamond 1.0 or ispLEVER 8.1                                     |                                                                    |                                                                  |  |

| Design Tool             | Synthesis               | Synopsys S                                                      | ynplify Pro for Lattice D-2                                        | 2009.12L-1                                                       |  |

| Support                 | Simulation              | Aldec A                                                         | Active-HDL 8.2 Lattice Ed                                          | lition II                                                        |  |

|                         | Simulation              | Mentor Graphics ModelSim SE 6.3F                                |                                                                    |                                                                  |  |

Table 1-3. NCO IP core for LatticeECP2 Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |  |

| Core                    | FPGA Families Supported | LatticeECP2                                                     |                                                                    |                                                                  |  |

| Requirements            | Minimal Device Needed   | LFE2-6E                                                         |                                                                    |                                                                  |  |

|                         | Targeted Device         | LFE2-50E-7F672C                                                 |                                                                    |                                                                  |  |

| _                       | LUTs                    | 100                                                             | 300                                                                | 300                                                              |  |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 1                                                                  | 3                                                                |  |

|                         | Registers               | 100                                                             | 300                                                                | 500                                                              |  |

|                         | MULT18X18ADDSUB         | 2                                                               | 0                                                                  | 4                                                                |  |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |  |

| Design Tool<br>Support  | Synthesis               | Synopsys Synplify Pro for Lattice D-2009.12L-1                  |                                                                    |                                                                  |  |

|                         | Simulation              | Aldec A                                                         | ctive-HDL 8.2 Lattice Ed                                           | lition II                                                        |  |

|                         | Simulation              | Mento                                                           | r Graphics ModelSim SE                                             | 6.3F                                                             |  |

Table 1-4. NCO IP core for LatticeSC Devices Quick Facts

|                           |                        | NCO IP Configuration                                            |                                                                    |                                                                 |  |

|---------------------------|------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------|--|

|                           |                        | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase res-<br>olution, 16 channe |  |

| Core FPGA Families Suppor |                        |                                                                 | LatticeSC                                                          |                                                                 |  |

| Requirements              | Minimal Device Needed  | LFSC3GA15E                                                      |                                                                    |                                                                 |  |

|                           | Targeted Device        | LFSC3GA25E-7F900C                                               |                                                                    |                                                                 |  |

|                           | LUTs                   | 2200                                                            | 300                                                                | 5200                                                            |  |

| Resource<br>Utilization   | sysMEM EBRs            | 3                                                               | 1                                                                  | 3                                                               |  |

|                           | Registers              | 1100 300 26                                                     |                                                                    | 2600                                                            |  |

|                           | MULT18X18ADDSUB        |                                                                 | N/A                                                                |                                                                 |  |

|                           | Lattice Implementation | Dia                                                             | amond 1.0 or ispLEVER                                              | 8.1                                                             |  |

| Design Tool               | Synthesis              | Synopsys S                                                      | ynplify Pro for Lattice D                                          | -2009.12L-1                                                     |  |

| Support                   |                        | Aldec Active-HDL 8.2 Lattice Edition II                         |                                                                    |                                                                 |  |

|                           | Simulation             | Mento                                                           | Mentor Graphics ModelSim SE 6.3F                                   |                                                                 |  |

Table 1-5. NCO IP core for LatticeSCM Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |  |

| Core                    | FPGA Families Supported |                                                                 | LatticeSCM                                                         |                                                                  |  |

| Requirements            | Minimal Device Needed   | vice Needed LFSCM3GA15EP1                                       |                                                                    |                                                                  |  |

|                         | Targeted Device         | LFSCM3GA25EP1-7F900C                                            |                                                                    |                                                                  |  |

| <b>D</b>                | LUTs                    | 2200                                                            | 300                                                                | 5200                                                             |  |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 1                                                                  | 3                                                                |  |

|                         | Registers               | 1100                                                            | 300                                                                | 2600                                                             |  |

|                         | MULT18X18ADDSUB         |                                                                 | N/A                                                                |                                                                  |  |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |  |

| Design Tool             | Synthesis               | Synopsys Sy                                                     | ynplify Pro for Lattice D-                                         | 2009.12L-1                                                       |  |

| Support                 |                         | Aldec Active-HDL 8.2 Lattice Edition II                         |                                                                    |                                                                  |  |

|                         | Simulation              | Mento                                                           | Graphics ModelSim SE                                               | 6.3F                                                             |  |

Table 1-6. NCO IP core for LatticeXP Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |

| Core                    | FPGA Families Supported |                                                                 | LatticeXP                                                          |                                                                  |

| Requirements            | Minimal Device Needed   | LFXP3E                                                          |                                                                    |                                                                  |

| Targeted Device         |                         |                                                                 | LFXP20E-5F484C                                                     |                                                                  |

| D                       | LUTs                    | 1800                                                            | 300                                                                | 3800                                                             |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 2                                                                  | 5                                                                |

|                         | Registers               | 800 300 1                                                       |                                                                    | 1900                                                             |

|                         | MULT18X18ADDSUB         |                                                                 | N/A                                                                |                                                                  |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |

| Design Tool             | Synthesis               | Synopsys S                                                      | ynplify Pro for Lattice D-                                         | 2009.12L-1                                                       |

| Support                 |                         | Aldec A                                                         | ctive-HDL 8.2 Lattice Ed                                           | dition II                                                        |

|                         | Simulation              | Mento                                                           | r Graphics ModelSim SE                                             | 6.3F                                                             |

Table 1-7. NCO IP core for LatticeECP2M Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |

| Core                    | FPGA Families Supported |                                                                 | LatticeECP2M                                                       |                                                                  |

| Requirements            | Minimal Device Needed   | vice Needed LFE2M20E                                            |                                                                    |                                                                  |

|                         | Targeted Device         | LFE2M-35E-7F484C                                                |                                                                    |                                                                  |

| _                       | LUTs                    | 100                                                             | 300                                                                | 300                                                              |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 1                                                                  | 3                                                                |

|                         | Registers               | 100                                                             | 300                                                                | 500                                                              |

|                         | MULT18X18ADDSUB         | 2                                                               | 0                                                                  | 4                                                                |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |

| Design Tool             | Synthesis               | Synopsys S                                                      | ynplify Pro for Lattice D-                                         | 2009.12L-1                                                       |

| Support                 |                         | Aldec A                                                         | active-HDL 8.2 Lattice Ed                                          | lition II                                                        |

|                         | Simulation              | Mento                                                           | r Graphics ModelSim SE                                             | 6.3F                                                             |

Table 1-8. NCO IP core for LatticeXP2 Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |  |  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|--|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |  |  |

| Core                    | FPGA Families Supported |                                                                 | LatticeXP2                                                         |                                                                  |  |  |

| Requirements            | Minimal Device Needed   | LFXP2-5E                                                        |                                                                    |                                                                  |  |  |

|                         | Targeted Device         | LFXP2-17E-7F484CES                                              |                                                                    |                                                                  |  |  |

| _                       | LUTs                    | 100                                                             | 300                                                                | 300                                                              |  |  |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 1                                                                  | 3                                                                |  |  |

|                         | Registers               | 100                                                             | 300                                                                | 500                                                              |  |  |

|                         | MULT18X18ADDSUB         | 2                                                               | 0                                                                  | 4                                                                |  |  |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |  |  |

| Design Tool             | Synthesis               | Synopsys Sy                                                     | ynplify Pro for Lattice D-2                                        | 2009.12L-1                                                       |  |  |

| Support                 |                         | Aldec A                                                         | ctive-HDL 8.2 Lattice Ed                                           | lition II                                                        |  |  |

|                         | Simulation              | Mento                                                           | Mentor Graphics ModelSim SE 6.3F                                   |                                                                  |  |  |

Table 1-9. NCO IP core for LatticeECP3 Devices Quick Facts

|                         |                         | NCO IP Configuration                                            |                                                                    |                                                                  |  |

|-------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|--|

|                         |                         | Constant FSK/PSK<br>with 32bit phase res-<br>olution, 1 channel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 1 chan-<br>nel | Variable FSK/PSK<br>with 32bit phase<br>resolution, 16<br>channe |  |

| Core                    | FPGA Families Supported |                                                                 | LatticeECP3                                                        |                                                                  |  |

| Requirements            | Minimal Device Needed   | d LFE3-35EA                                                     |                                                                    |                                                                  |  |

|                         | Targeted Device         | LFE3-95E-7FN672CES                                              |                                                                    |                                                                  |  |

| _                       | LUTs                    | 100                                                             | 300                                                                | 400                                                              |  |

| Resource<br>Utilization | sysMEM EBRs             | 3                                                               | 1                                                                  | 3                                                                |  |

|                         | Registers               | 100                                                             | 300                                                                | 500                                                              |  |

|                         | MULT18X18C              | 4                                                               | 0                                                                  | 8                                                                |  |

|                         | Lattice Implementation  | Dia                                                             | mond 1.0 or ispLEVER 8                                             | 3.1                                                              |  |

| Design Tool             | Synthesis               | Synopsys Sy                                                     | nplify Pro for Lattice D-2                                         | 2009.12L-1                                                       |  |

| Support                 |                         | Aldec A                                                         | ctive-HDL 8.2 Lattice Ed                                           | lition II                                                        |  |

|                         | Simulation              | Mentor                                                          | Mentor Graphics ModelSim SE 6.3F                                   |                                                                  |  |

# **Features**

- Supports single or multi channel operation up to 16 channels

- Run time variable phase increment input  $\Delta\theta$  and phase offset input  $\varphi$

- Up to 32-bit user-configurable phase resolution

- Up to 20-bit user-configurable quantizer resolution

- Up to 32-bit user-configurable amplitude resolution

- User-configurable memory saving architectures 1/2 wave, 1/4 wave or full wave

- · User-selectable sum of angles (SOA) optimization for memory saving

- Up to 4-bit user-selectable phase dithering correction

- User-selectable trigonometric correction for SFDR improvement

- · Option for truncating or rounding the quantizer output when neither dithering nor trigonometric correction is used.

- User-selectable QAM mode support

- Provides high-SFDR up to 115 dB

- Provides sine, cosine or quadrature outputs.

- · User configurable output polarity

# **Functional Description**

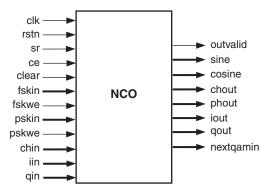

This chapter provides a functional description of the NCO IP core. Figure 2-1 shows a top-level inteface diagram for the NCO IP core.

Figure 2-1. Top-level Interface Diagram for NCO IP Core

# **Principle of NCO**

The NCO generates a sine waveform using the concept of direct digital synthesis. In direct digital synthesis, the samples of the sine wave are stored in memory and are read out to generate the output sine wave. The frequency of the output sine wave is controlled by the clock speed and appropriate skipping of intermediate data points. In the simplest scenario, the sampled data for one full wave period is stored in memory and is directly used for the output. However, other enhanced methods are frequently used to reduce the memory size requirements. For example, only a half or a quarter cycle of the waveform could be stored in memory and the memory address and output sign could be manipulated to get the full cycle waveform. Another useful technique for memory reduction is to consider the input angle as the sum of a coarse angle and a fine angle and compute the output from coarse and fine look-up tables using the sum of angles trigonometric identity.

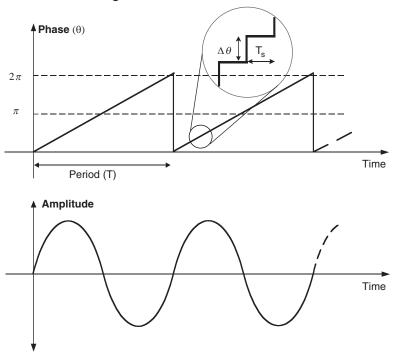

The simplest full wave NCO is considered first to explain the concepts and bring out the notations. The full wave corresponding to one period of the sine wave is divided into N segments. The incremental angle for each segment, denoted as  $\Delta\theta$ , is equal to  $2\pi/N$  and the phase values corresponding to one period are given by:

$$\theta_i = \frac{2\pi i}{N}$$

$i = 0, 1, 2, ..., N-1$  (1)

The output values corresponding to the phase sequence, given in Equation 2, are stored in the look-up table. Figure 2 shows the mapping of angle to sine waveform.

$$d_{i} = \sin \theta_{i} = \sin \left[ \frac{2\pi i}{N} \right] \tag{2}$$

The phase index, i is generated either sequentially or in increments and used to address the memory look-up table. The output of the look-up table is the sine wave sample. The index increment can be any value greater than zero, including fractional values.

Figure 2-2. Mapping of Linear Phase Angle to Sine Wave

# **Lattice NCO Implementation**

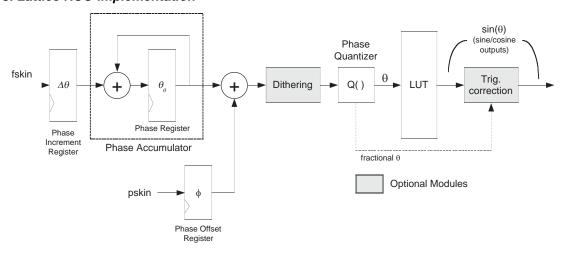

The key elements of a simple NCO are the phase accumulator and waveform look-up table. The phase accumulator adds a constant phase increment stored in the phase increment register to the accumulated phase at every clock cycle. The accumulated phase provides addresses for the look-up table. The accumulated phase is usually quantized before addressing the look-up table to allow for fractional phase index increments.

The Lattice NCO implementation is shown in Figure 2-3. This figure shows a single channel NCO, with FSK (Frequency Shift Keying) and PSK (Phase Shift Keying) inputs and a full wave look-up table. It also shows optional modules for dithering and trigonometric correction. The functional blocks of NCO IP are described in the following sections.

Figure 2-3. Lattice NCO Implementation

### Phase Increment Register (for FSK)

The phase increment register stores the phase value ( $\Delta\theta$ ) that gets added up to the accumulated phase at every clock cycle. The phase increment linearly decides the frequency of the output signal. Hence, this input can be used for frequency shift keying (FSK) modulation. The phase increment is either fixed or read dynamically from an input port, fskin, depending on how the NCO is configured. The output frequency is always a fraction of the clock frequency of the system.

### **Phase Accumulator**

The phase accumulator computes the phase angle value that is used to address the look-up tables used for the output sine signal generation. The phase angle at any cycle is equal to the phase angle at the last cycle plus the phase increment. For cycle i,  $\theta_i = \theta_{i-1} + \Delta\theta$ . The width of the accumulator is specified by the user parameter, "Phase resolution". For a given accumulator width, phase resolution is highest when the phase increment is equal to 1 and reduces for values greater than 1.

### **Phase Shift Keying**

A constant phase input is added to the accumulated phase before addressing the look-up table. This is useful for implementing phase shift keying (PSK) modulation of the NCO output. The user can choose no phase offset, a fixed phase offset or a variable phase offset (PSK). The variable offset is applied through the PSK input (pskin). Any phase offset that is added causes a shift in the phase angle and a corresponding linear phase shift in the output sine signal.

#### Quantizer

The output of phase accumulator (or the optional PSK or dithering module) drives the quantizer. The quantizer scales down the accumulator output to reduce the size of the look-up table. Assuming the look-up able has integer resolution, the quantizer provides a mechanism for fractional phase increments. The Quantizer output width decides the depth of the look-up table and is normally less than the accumulator output width. This allows high precision accumulation operation while using less memory.

### Look-up Table

The central part of the NCO is the look-up table which stores the values of the sine wave corresponding to equally spaced phase angles in the  $(0,2\pi)$  interval. If the Wave size parameter is equal to "half" or "quarter", sine wave samples corresponding to  $(0,\pi)$  or  $(0,\pi/2)$  respectively are stored in the look-up table. As the cosine of an angle can be derived from the sine of a shifted angle, the cosine value, if required, is read from the same look-up table by manipulating the address. The depth of the look-up table is always a power of 2 and is determined by the user-defined parameter Quantizer resolution. The width of the look-up table is, in most cases, equal to the output width. The look-up table is implemented using block or distributed memories, which is selected by the user parameter Memory type. The memory is addressed by the phase angle index, which is generated by the accumulator and quantizer blocks.

Half-wave storage reduces the memory requirement by half, but uses slightly more logic and increases the latency by one cycle. Except for very small look-up table configurations, the user may better choose half-wave storage to reduce memory usage. The user can also choose a quarter-wave storage to reduce memory by another half (half of what is needed for half-wave storage). In the quarter-wave case, however, the latency increases by 1 cycle and additional logic is used compared to half-wave implementation.

### **Sum-of-Angles Memory Reduction**

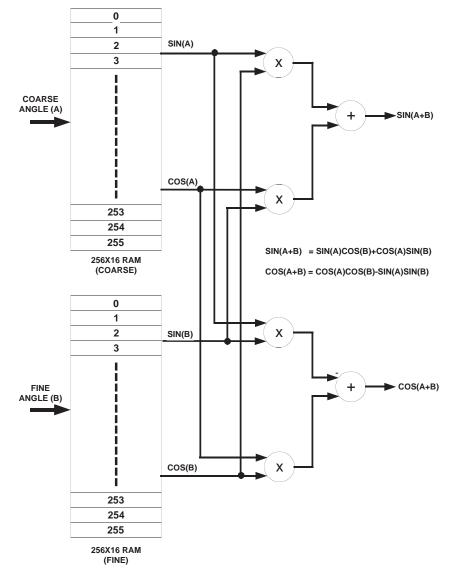

As the sine wave samples are stored in memory in direct digital synthesis NCOs, increasing the phase resolution of the output leads to corresponding increase in the size of the look-up table. The amount of memory required can be greatly reduced by making use of the "sum of angles" trigonometric identity and by using additional multipliers and adders after the memory output. This is achieved by dividing the angle space into coarse sub-divisions and then writing the phase angle as a sum of the nearest coarse angle and an additive corrective angle (fine angle).

Consider Equation 1 that relates phase angle to an integer angle index. The phase angle resolution of N that is used in that equation can be achieved by the following method. Define the following two sets of angles: coarse and fine, by choosing C and F to satisfy the equation  $C^*F=N$ .

Coarse angle set:

$$c_j = \frac{2\pi j}{C}$$

$j = 0, 1, 2, ..., C-1$  (3)

Fine angle set:

$$f_k = \frac{2\pi k}{CF}$$

$k = 0, 1, 2, ..., F-1$  (4)

Any phase angle  $\theta_i$  of Equation 1 can be written as a sum of an angle in the coarse set and one in the fine set as:

$$\theta_i = c_x + f_y$$

where  $x = i \text{ div } F \text{ and } y = i \text{ mod } F.$

(5)

The sine and cosine values of  $\theta_i$  can be computed using the sine and cosine values of  $c_x$  and  $f_y$  using the following trigonometric identity:

$$\begin{split} &\sin{(\theta_i)} = \sin(c_x + f_y) &= \sin(c_x)^* \cos(f_y) + \cos(c_x)^* \sin(f_y) \\ &\cos{(\theta_i)} = \cos(c_x + f_y) = \cos(c_x)^* \cos(f_y) - \sin(c_x)^* \sin(f_y) \end{split}$$

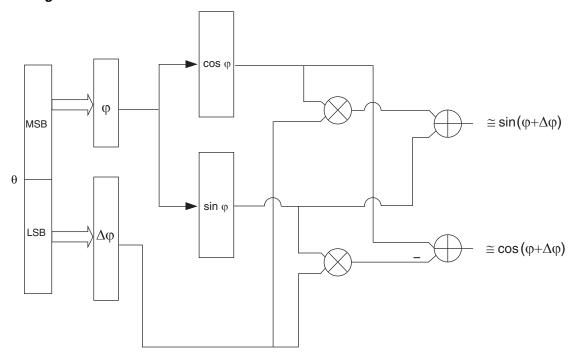

The look-up tables need only to store the sine and cosine values for coarse and fine phase angle sets only. An implementation of the sum of angles scheme is shown in Figure 2-4.

Figure 2-4. Sum of Angles Memory Reduction

This sum of angle scheme uses four multipliers and two adders after the look-up table. However, the memory used is much less compared with the full-wave scheme without sum of angles reduction. For a typical example of 16-bit quantizer resolution, sum of angles scheme can lead to more than 98% memory saving, compared to the full-wave implementation.

# **Improving Quality of Output**

A common measure of the output quality of NCO is the Spurious Free Dynamic Range (SFDR). This roughly indicates the degree of power separation between the main lobe and the next strongest side lobe in the power spectral density plot. The SFDR can be improved using either phase dithering or trigonometric correction. Phase dithering diffuses the concentration of phase quantization noise by adding a small random value to the accumulated phase before quantization. Trigonometric correction serves to improve the SFDR in a more deterministic way by adding a correction factor computed from the discarded LSB bits, to the output. The SFDR for the NCO output without dithering or trigonometric correction is approximately equal to 6\*Quantizer resolution.

### **Phase Dithering**

Truncation in phase address output from accumulator, results in amplitude errors at the output of the sine or cosine waveforms. These errors are periodic in nature regardless of the frequency of operation. Due to the periodicity of these errors in time, they appear as spurious frequencies in the frequency spectrum. This reduces the SFDR of the output signal. In order to improve the SFDR, random phase error is introduced in the least significant bits of the look up table address. Introduction of this randomness minimizes the periodicity of the errors in time domain, resulting in reduced strength of the spurious frequencies in frequency spectrum. This SFDR improvement is achieved at the cost of reduced signal-to-noise ratio (SNR) at the output. Phase dithering is implemented by adding a random number to the phase address output of the accumulator before it is given to the quantizer. The word length of the random number is user programmable based on the parameter Dithering bits.

### **Trigonometric Correction**

If the SFDR requirements are more stringent and cannot be met by the phase dithering option, then trigonometric phase correction implementation should be used. This implementation improves SFDR by 46 dB over the no-phase-correction implementation and by 34 dB over the phase dithering implementation. The phase correction is implemented on the output samples from the look-up table memories as shown in Figure 2-5. In this implementation the truncated LSBs of the phase accumulator are used for phase correction using trigonometric properties as explained below:

For any  $\varphi$  and a  $\Delta \varphi < \pi/2$ ,

$$\sin (\phi + \Delta \phi) \cong \sin (\phi) + \Delta \phi * \cos (\phi)$$

$$cos (\phi + \Delta \phi) \cong cos (\phi) - \Delta \phi * sin (\phi)$$

This implementation requires two additional multipliers and two adders and one constant multiplier as shown in the figure.

Figure 2-5. Trigonometric Phase Correction

### **Multi-channel NCO**

In multi-channel operation, the NCO can generate outputs for up to 16 channels. All these outputs will timeshare the output ports. The multi-channel implementation of the NCO contains all the functional blocks required by the single channel NCO. In addition to those blocks, it uses memories for storing the phase increment values, phase offset values and phase accumulator output values for each channel.

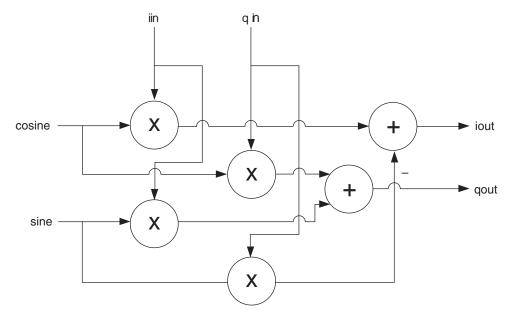

# **Quadrature Amplitude Modulation (QAM)**

In addition to frequency and phase modulations, this NCO can also be used for quadrature amplitude modulation (QAM). These modulations are ubiquitous in wireless and wireline communications systems. Four multipliers and two adders are required for implementing QAM. The QAM implementation is shown in Figure 2-6.

Figure 2-6. QAM Implementation

# **Signal Descriptions**

Table 2-1. Interface Signal Descriptions

| Port          | Bits          | I/O          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All Configura | ations        | 1            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| clk           | 1             | I            | System clock (reference clock for input and output data).                                                                                                                                                                                                                                                                                                                                                                                                  |

| rstn          | 1             | I            | System wide asynchronous active low reset signal.                                                                                                                                                                                                                                                                                                                                                                                                          |

| sine          | 4 - 32        | 0            | Sine output data in 2's complement form. This port can be optionally omitted if either cosine port or QAM ports (iout and qout) are selected.                                                                                                                                                                                                                                                                                                              |

| cosine        | 4 - 32        | 0            | Cosine output data in 2's complement form. This port can be optionally omitted if either sine port or QAM ports (iout and qout) are selected.                                                                                                                                                                                                                                                                                                              |

| A For FSK M   | ode only (wh  | en the para  | meter FSK input = "Variable")                                                                                                                                                                                                                                                                                                                                                                                                                              |

| fskin         | 3 - 31        | I            | Frequency shift keying input data. This unsigned value becomes the phase increment factor for the phase accumulator and decides the output frequency. The value at this port is read only when fskwe is high.                                                                                                                                                                                                                                              |

| fskwe         | 1             | I            | Write enable strobe for fskin data.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| For PSK Mod   | de only (wher | the parame   | eter PSK input = "Variable")                                                                                                                                                                                                                                                                                                                                                                                                                               |

| pskin         | 3 - 32        | I            | Phase shift keying input data. This unsigned value is used as offset to accumulated phase and is normally used to implement phase shift keying modulation. The value at this port is read only when pskwe is high.                                                                                                                                                                                                                                         |

| pskwe         | 1             | I            | Write enable strobe for pskin data.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| For Multi-cha | annel Mode o  | nly (when tl | ne parameter Multi channel = "Yes")                                                                                                                                                                                                                                                                                                                                                                                                                        |

| chin          | 1 - 4         | Ι            | This port is used when the number of channels is more than one and either or both $\texttt{PSK}$ input and $\texttt{FSK}$ input parameters are configured as "Variable". The value in $\texttt{chin}$ port associates the channel number for the current $\texttt{fskin}$ or $\texttt{pskin}$ ports. The width of this port depends upon the number of channels and is equal to the next higher integer value of $\texttt{log}_2$ of (Number of Channels). |

| chout         | 1 - 4         | 0            | This output is present if the NCO operates in multi-channel mode. The value at this port indicates the channel number for which data samples are given at the output currently. The width of this port depends upon the number of channels and is equal to the next higher integer value of log <sub>2</sub> of (Number of Channels).                                                                                                                      |

| For QAM Mo    | de only (whe  | n the param  | eter QAM Mode = "Yes")                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| iin           | 4 - 18        | I            | I input for Quadrature Amplitude Modulation. The width is defined by the parameter QAM input port width.                                                                                                                                                                                                                                                                                                                                                   |

| qin           | 4 - 18        | I            | Q input for Quadrature Amplitude Modulation. The width is defined by the parameter QAM input port width.                                                                                                                                                                                                                                                                                                                                                   |

| iout          | 4 - 32        | 0            | I component of the QAM output. is equal to Output width plus QAM input port width.                                                                                                                                                                                                                                                                                                                                                                         |

| qout          | 4 - 32        | 0            | Q component of the QAM output. The width of this port is equal to Output width plus QAM input port width. The qout port is a user-selectable output.                                                                                                                                                                                                                                                                                                       |

| nextqamin     | 1-4           | 0            | This output port gives the channel number for the next QAM input signal (iin or qin). This optional signal is available only when Multi-channel is selected.                                                                                                                                                                                                                                                                                               |

| Optional I/Os | 3             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| се            | 1             | I            | Clock enable signal. This signal has the highest priority after rstn. The NCO operation freezes for as long as ce is held low. This optional signal should be selected only when required as it leads to increased core size.                                                                                                                                                                                                                              |

| sr            | 1             | I            | Synchronous reset signal. When asserted all internal registers are reset. The optional signal ce, if used, must be held high, for sr to be effective. This optional signal should be selected only when required as it leads to increased core size.                                                                                                                                                                                                       |

| clear         | 1             | I            | Accumulator clear signal. If high, it clears the phase accumulator and restarts the sine output from zero or the programmed phase offset (PSK offset).                                                                                                                                                                                                                                                                                                     |

Table 2-1. Interface Signal Descriptions (Continued)

| Port     | Bits | I/O | Description                                                                                                                          |

|----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| phout    | 3-32 | 0   | Phase output. This optional output provides the phase value corresponding to the current sine or cosine output (in unsigned format). |

| outvalid | 1    | 0   | Output valid. This optional output signal signifies the presence of a valid output at the output data busses (sine and/or cosine).   |

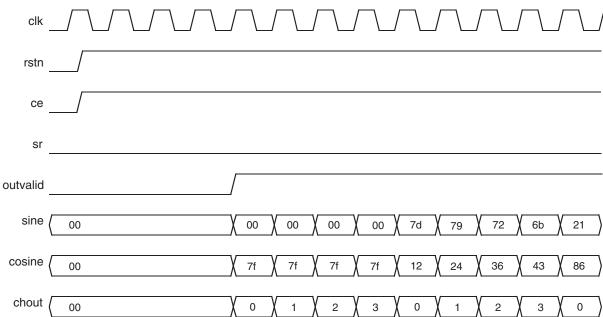

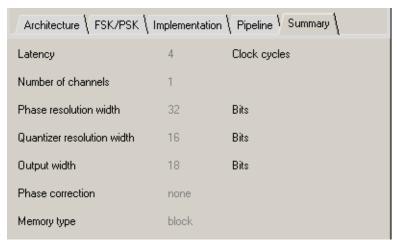

# Latency

The latency for NCO varies depending on different parameter settings. It is displayed in the summary page of the NCO IP GUI. Latency for NCO is defined as the number of clock cycles required for changes to either fskin or pskin to be reflected in sine or cosine outputs. When both FSK input and PSK input are defined as "constant", then the latency is the number of clock cycles for valid outputs (sine or cosine) to appear after rstn is deasserted. For the sample configuration in the timing diagram Figure 2-7, the latency is three cycles.

# **Timing Diagrams**

The I/O timing diagrams for single channel and multi-channel NCOs are given in Figure 2-7 and Figure 2-8 respectively.

Figure 2-7. Timing Diagram for Single Channel NCO

Figure 2-8. Timing Diagram for Multi-Channel NCO

# **Parameter Settings**

The IPexpress<sup>™</sup> tool is used to create IP and architectural modules in the Diamond and ispLEVER software. Refer to "IP Core Generation" on page 27 for a description on how to generate the IP.

Table 3-1 provides the list of user configurable parameters for the NCO IP core. The parameter settings are specified using the NCO IP core Configuration GUI in IPexpress. The numerous NCO parameter options are partitioned across multiple GUI tabs as shown in this chapter.

Table 3-1. NCO IP Core Configuration Parameters

| Parameter            | Range/Options                                                                                                                                                                    | Default<br>Value |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Multi-channel Mode   | ·                                                                                                                                                                                |                  |

| Multi-channel        | Yes, No                                                                                                                                                                          | No               |

| Number of channels   | 2 to 16                                                                                                                                                                          | 16               |

| Wave Characteristics | ·                                                                                                                                                                                |                  |

| Wave size            | full, half or quarter                                                                                                                                                            | full             |

| Sum of angles        | Yes, No                                                                                                                                                                          | Yes              |

| Phase resolution     | 3 to 32 (for non Trigonometric correction); 32 (for Trigonometric correction).                                                                                                   | 32               |

| Quantizer resolution | 3 to 16 if sum of angles is not used;<br>6 to 20, if sum of angles is used;<br>12, if Trig. correction is used. The<br>maximum is limited by Phase reso-<br>lution in all cases. | 16               |

| Output width         | 18, if Trigonometric correction; 4 to 18, if sum of angles or QAM mode; otherwise 4 to 32.                                                                                       | 18               |

| Phase Correction     | <u> </u>                                                                                                                                                                         | 1                |

| Phase correction     | None, Dithering, Trigonometric                                                                                                                                                   | None             |

| Rounding type        | Truncation, Nearest                                                                                                                                                              | Truncation       |

| Dithering bits       | 1 to 4                                                                                                                                                                           | 4                |

| QAM Mode             |                                                                                                                                                                                  |                  |

| QAM mode             | Yes, No                                                                                                                                                                          | No               |

| QAM input port width | 4 to 18                                                                                                                                                                          | 16               |

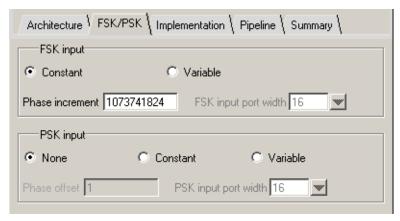

| FSK Mode             |                                                                                                                                                                                  |                  |

| FSK input            | Constant, Variable                                                                                                                                                               | Constant         |

| Phase increment      | 1 to 2^(Phase resolution-1)                                                                                                                                                      | 1073741824       |

| FSK input port width | 3 to (Phase resolution -1)                                                                                                                                                       | 16               |

| PSK Mode             |                                                                                                                                                                                  |                  |

| PSK input            | None, Constant, Variable}                                                                                                                                                        | None             |

| Phase offset         | 1 to 2^(Phase resolution)                                                                                                                                                        | 1                |

| PSK input port width | 3 to Phase resolution                                                                                                                                                            | 16               |

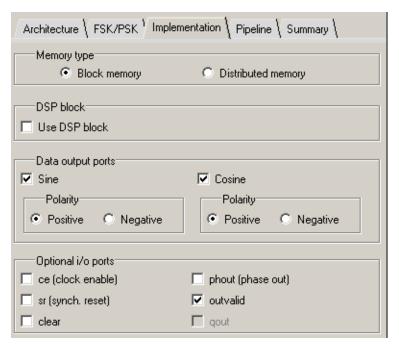

| Memory Type          |                                                                                                                                                                                  |                  |

| Memory type          | Block memory, Distributed memory                                                                                                                                                 | Block<br>memory  |

| DSP Block            |                                                                                                                                                                                  |                  |

| Use DSP block        | Yes, No                                                                                                                                                                          | Yes              |

Table 3-1. NCO IP Core Configuration Parameters (Continued)

| Parameter                                                  | Range/Options        | Default<br>Value |

|------------------------------------------------------------|----------------------|------------------|

| Data Output Ports                                          |                      |                  |

| Sine                                                       | Yes, No              | Yes              |

| Cosine                                                     | Yes, No              | Yes              |

| Sine Polarity                                              | {Positive, Negative} | Positive         |

| Cosine Polarity                                            | {Positive, Negative} | Positive         |

| Optional I/O Ports                                         |                      | -                |

| ce                                                         | Yes, No              | No               |

| sr                                                         | Yes, No              | No               |

| clear                                                      | Yes, No              | No               |

| phout                                                      | Yes, No              | No               |

| outvalid                                                   | Yes, No              | Yes              |

| qout                                                       | Yes, No              | No               |

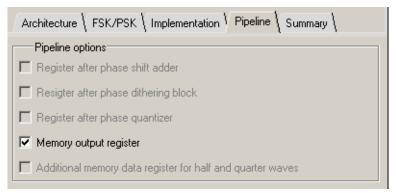

| Pipeline Options                                           |                      |                  |

| Register after phase shift adder                           | Yes, No              | No               |

| Register after phase dithering block                       | Yes, No              | No               |

| Register after phase quantizer                             | Yes, No              | No               |

| Memory output register                                     | Yes, No              | Yes              |

| Additional memory data register for half and quarter waves | Yes, No              | No               |

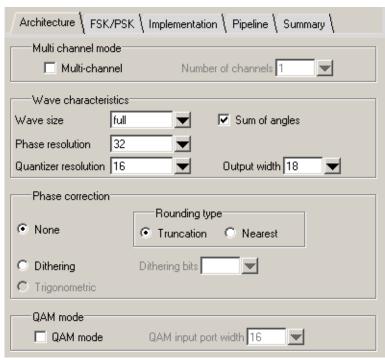

# **Architecture Tab**

Figure 3-1 shows the contents of the Architecture tab.

Figure 3-1. Architecture Tab

#### **Multi-channel Mode**

#### Multi-channel

Determines whether multiple channels are supported.

#### **Number of Channels**

Denotes the number of NCO channels. Valid only if Multi-channel is selected.

#### **Wave Characteristics**

#### **Wave Size**

Determines how much of the sine wave is stored in the look-up table.

### **Sum of Angles**

Determines whether sum of angles method is used for memory reduction.

#### **Phase Resolution**

Phase Resolution: Maximum phase resolution of the NCO expressed in bits. This also defines the accumulator width.

#### **Quantizer Resolution**

Phase quantizer resolution: The output of the phase accumulator is quantized to this resolution before addressing the trigonometric look-up table. This also determines the depth of the trigonometric look-up table. The maximum value supported is 16 bits without sum of angles usage and 20 bits if the sum of angles method is employed. This resolution must be less than or equal to Phase resolution.

#### **Phase Correction**

#### **Phase Correction**